## INTEGRATED CIRCUITS

Product specificationSupersedes data of 2003 Aug 07

2003 Oct 01

### SAA7824

#### CONTENTS

| 1      | FEATURES                                 |

|--------|------------------------------------------|

| 2      | GENERAL DESCRIPTION                      |

| 3      | ORDERING INFORMATION                     |

| 4      | QUICK REFERENCE DATA                     |

| 5      | BLOCK DIAGRAM                            |

| 6      | PINNING                                  |

| 7      | FUNCTIONAL DESCRIPTION                   |

| 7.1    | Data acquisition and HF data path        |

| 7.2    | Decoder part                             |

| 7.2.1  | Principle operating modes of the decoder |

| 7.2.2  | Decoder speed and crystal frequency      |

| 7.2.3  | Lock-to-disc mode                        |

| 7.2.4  | Standby modes                            |

| 7.3    | Crystal oscillator                       |

| 7.4    | Data slicer and bit clock regenerator    |

| 7.5    | DC offset cancellation                   |

| 7.5.1  | Offset cancellation                      |

| 7.5.2  | Reading back the DC offset value         |

| 7.6    | Demodulator                              |

| 7.6.1  | Frame sync protection                    |

| 7.6.2  | EFM demodulation                         |

| 7.7    | Subcode data processing                  |

| 7.7.1  | Q-channel processing                     |

| 7.7.2  | EIAJ 3 and 4-wire subcode (CD graphics)  |

|        | interface                                |

| 7.7.3  | V4 subcode interface                     |

| 7.7.4  | CD text interface                        |

| 7.8    | FIFO and error correction                |

| 7.8.1  | Flags output (CFLG)                      |

| 7.9    | Audio functions                          |

| 7.9.1  | De-emphasis and phase linearity          |

| 7.9.2  | Digital oversampling filter              |

| 7.9.3  | Concealment                              |

| 7.9.4  | Mute, full-scale, attenuation and fade   |

| 7.9.5  | Peak detector                            |

| 7.10   | Audio DAC interface                      |

| 7.10.1 | Internal dynamic element matching        |

|        | digital-to-analog converter              |

| 7.10.2 | External DAC interface                   |

| 7.11   | EBU interface                            |

| 7.11.1 | Format                                   |

| 7.12   | KILL features                            |

| 7.12.1 | The KILL circuit                         |

| 7.12.2 | Silence injection                        |

| 7.13   | Audio features off                       |

| 7.14   | The versatile pins interface             |

| 7.15   | Spindle motor control                    |

| 7.15.1 | Motor output modes                       |

| 7.15.2 | Spindle motor operating modes            |

|        |                                          |

| 7.15.3  | Loop characteristics                                        |

|---------|-------------------------------------------------------------|

| 7.15.4  | FIFO overflow                                               |

| 7.16    | Servo part                                                  |

| 7.16.1  | Diode signal processing                                     |

| 7.16.2  | Signal conditioning                                         |

| 7.16.3  | Focus servo system                                          |

| 7.16.4  | Radial servo system                                         |

| 7.16.5  | Off-track counting                                          |

| 7.16.6  | Track counting modes                                        |

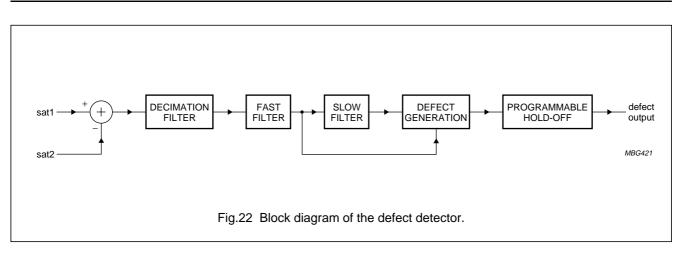

| 7.16.7  | Defect detection                                            |

| 7.16.8  | Off-track detection                                         |

| 7.16.9  | High-level features                                         |

| 7.16.10 | Driver interface                                            |

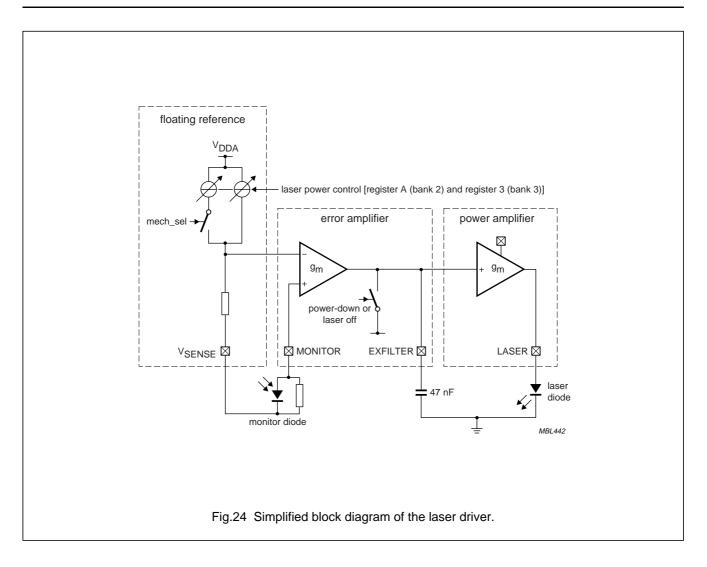

| 7.16.11 | Laser interface                                             |

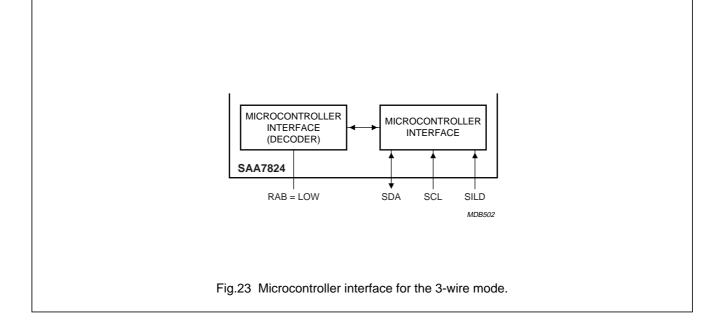

| 7.17    | Microcontroller interface                                   |

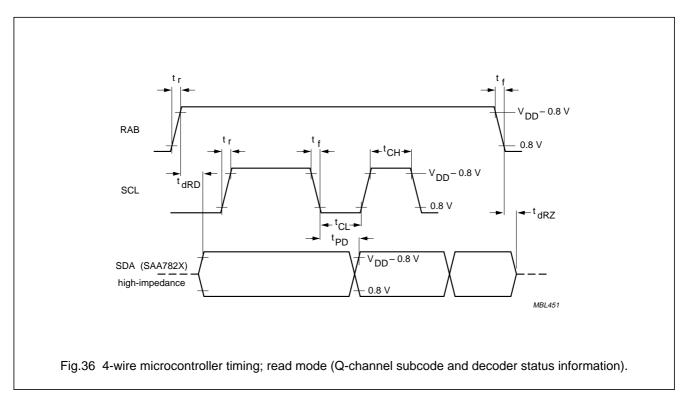

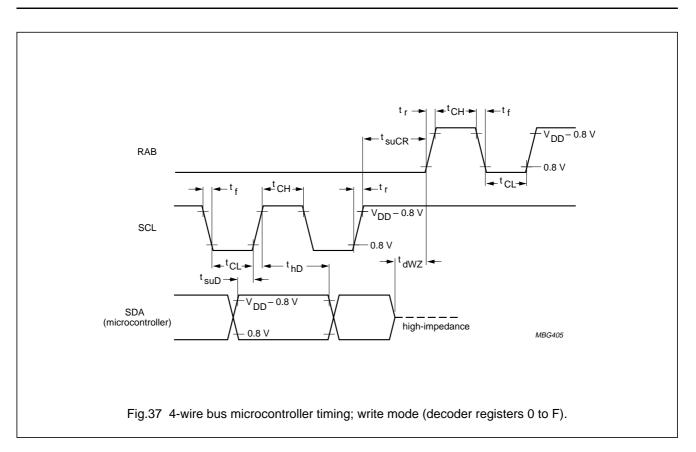

| 7.17.1  | Microcontroller interface (4-wire bus mode)                 |

| 7.17.2  | Microcontroller interface (I <sup>2</sup> C-bus mode)       |

| 7.17.3  | Decoder and shadow registers                                |

| 7.17.4  | Summary of functions controlled by decoder registers 0 to F |

| 7.17.5  | Summary of functions controlled by shadow                   |

| 1.11.5  | registers                                                   |

| 7.17.6  | Summary of servo commands                                   |

| 7.17.7  | Summary of servo command parameters                         |

| 8       | SUMMARY OF SERVO COMMAND                                    |

| 0       | PARAMETERS VALUES                                           |

| 9       | LIMITING VALUES                                             |

| 10      | CHARACTERISTICS                                             |

| 11      | OPERATING CHARACTERISTICS                                   |

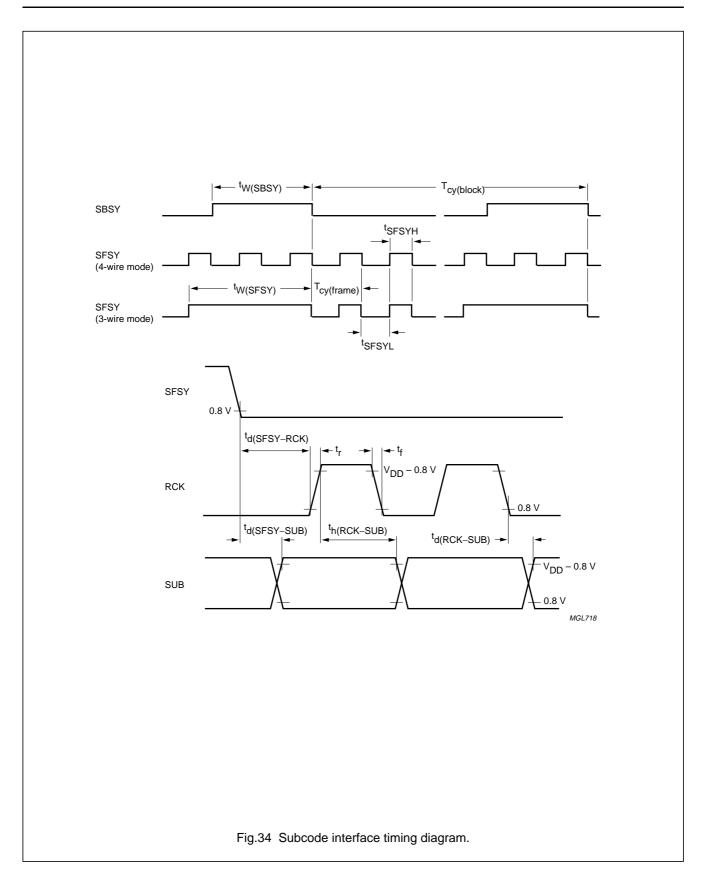

|         | (SUBCODE INTERFACE TIMING)                                  |

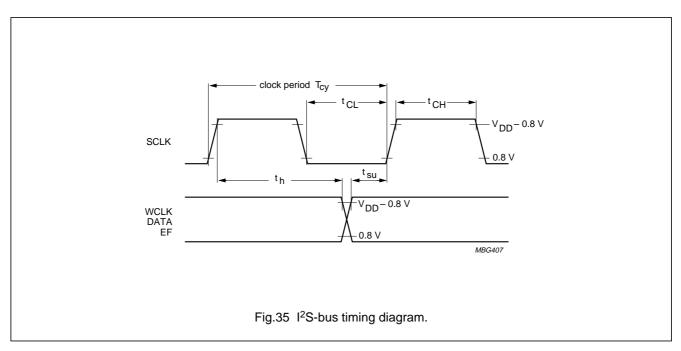

| 12      | OPERATING CHARACTERISTICS (I <sup>2</sup> S-BUS             |

|         | TIMING)                                                     |

| 13      | OPERATING CHARACTERISTICS                                   |

|         | (MICROCONTROLLER INTERFACE TIMING)                          |

| 14      | APPLICATION INFORMATION                                     |

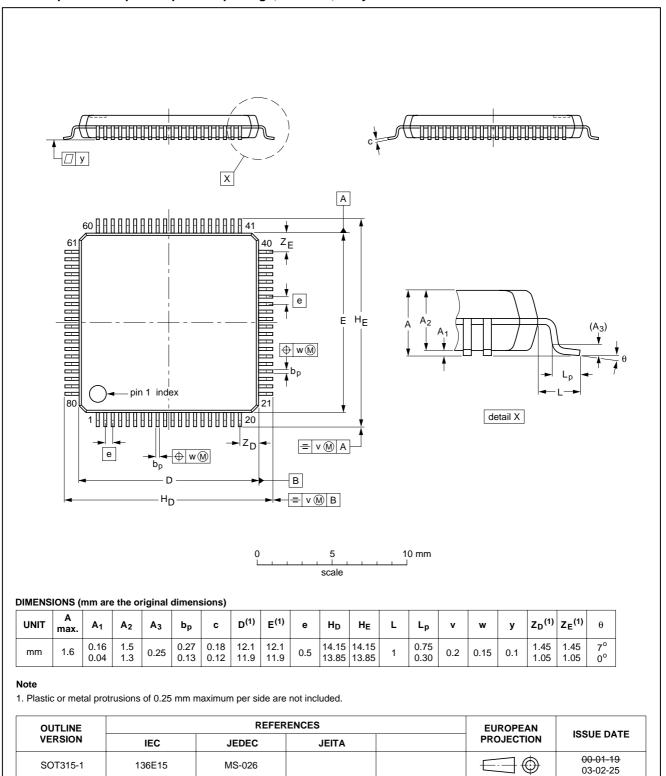

| 15      | PACKAGE OUTLINE                                             |

| 16      | SOLDERING                                                   |

| 16.1    | Introduction to soldering surface mount                     |

|         | packages                                                    |

| 16.2    | Reflow soldering                                            |

| 16.3    | Wave soldering                                              |

| 16.4    | Manual soldering                                            |

| 16.5    | Suitability of surface mount IC packages for                |

|         | wave and reflow soldering methods                           |

| 17      | DATA SHEET STATUS                                           |

| 18      | DEFINITIONS                                                 |

| 19      | DISCLAIMERS                                                 |

| 20      | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS             |

## SAA7824

### 1 FEATURES

- Decoder and servo parts are based upon the SAA732X design (the original features are maintained)

- Software compatibility is maintained with the SAA732X by using a similar register structure (new features are controlled from new shadow registers)

- 1×, 2× and 4× speed

- LF (servo) signals converted to digital representations by 6 oversampling bitstream ADCs

- HF part summed from signals D1 to D4 and converted into a digital signal by a data slicer

- On-chip buffering and filtering of the diode signals from the mechanism for signal optimization

- Selectable DC offset cancellation of quiescent mechanism voltages and dark currents

- On-chip laser power control (up to 120 mA)

- Laser on/off control, including 'soft' start control (zero to nominal power in 1 ms)

- Monitor control and feedback circuit to maintain nominal output power throughout laser life

- Dynamic element matching DAC with minimum external components

- DAC performance of –80 dB Total Harmonic Distortion + Noise (THD + N) and 90 dB Signal-to-Noise Ratio (S/N) A-weighted

- Separate left and right channel digital silence detection available on the KILL pins

- Digital silence detection on internal data and loopback (external) data

- 5 versatile pins, 2 inputs and 3 outputs

- Integrated CD text decoder with separate microcontroller interface

- Dedicated 4 MHz or 12 MHz clock output for microcontroller (configurable)

- Configured for N-sub monitor diode

- On-chip clock multiplier allows the use of an 8.4672 MHz crystal or ceramic resonator

- The M1 version has an EBU mute function which allows independent muting of data being transmitted over the EBU interface whilst maintaining the SPDIF frame structure.

#### 2 GENERAL DESCRIPTION

This document covers versions M0 and M1 of the CD audio decoder IC.

The SAA7824 is a CD audio decoder IC which combines the function of the SAA732X IC with the pre-amplifier and laser control functions previously found in the TZA102X IC. The design is intended to reduce the external component count and hence the Bill Of Material (BOM).

Supply of this Compact Disc IC does not convey an implied license under any patent right to use this IC in any Compact Disc application.

### SAA7824

#### **3 ORDERING INFORMATION**

| TYPE      | PACKAGE |                                                                                    |          |  |  |  |  |  |

|-----------|---------|------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| NUMBER    | NAME    | NAME DESCRIPTION VERSION                                                           |          |  |  |  |  |  |

| SAA7824HL | LQFP80  | plastic low profile quad flat package; 80 leads; body $12 \times 12 \times 1.4$ mm | SOT315-1 |  |  |  |  |  |

#### 4 QUICK REFERENCE DATA

| SYMBOL               | PARAMETER                         | CONDITIONS | MIN. | TYP.   | MAX. | UNIT |

|----------------------|-----------------------------------|------------|------|--------|------|------|

| V <sub>DDD</sub>     | digital supply voltage            |            | 1.65 | 1.8    | 1.95 | V    |

| V <sub>DDA</sub>     | analog supply voltage             |            | 3.0  | 3.3    | 3.6  | V    |

| I <sub>DD(tot)</sub> | total supply current              | n = 1 mode | -    | 38     | -    | mA   |

|                      |                                   | n = 2 mode | _    | 39     | -    | mA   |

|                      |                                   | n = 4 mode | _    | 40     | -    | mA   |

| f <sub>xtal</sub>    | crystal frequency                 |            | _    | 8.4672 | -    | MHz  |

| T <sub>amb</sub>     | ambient temperature               |            | 0    | -      | 70   | °C   |

| T <sub>stg</sub>     | storage temperature               |            | -55  | -      | +125 | °C   |

| S/N <sub>DAC</sub>   | onboard DAC signal-to-noise ratio |            | -    | 90     | -    | dB   |

### SAA7824

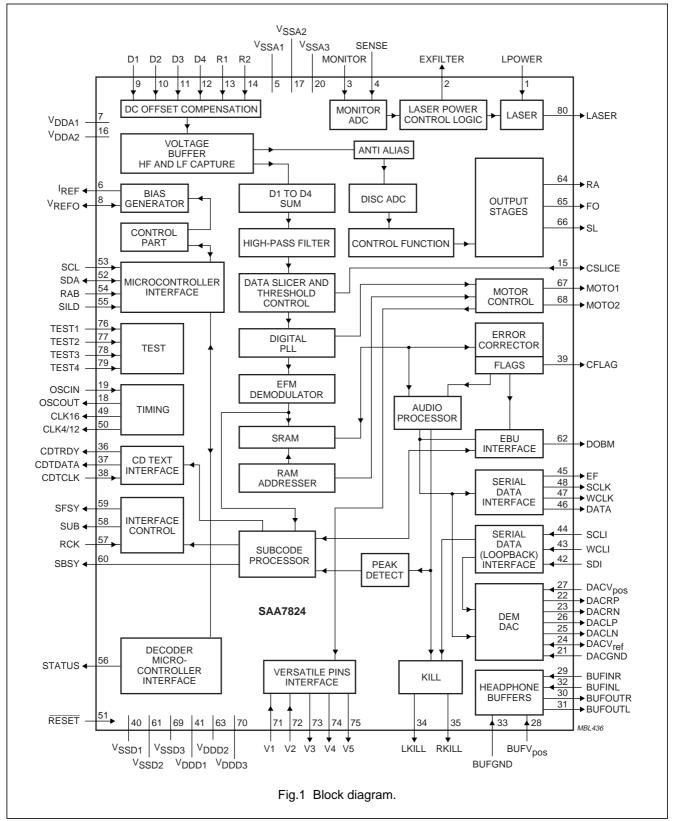

### 5 BLOCK DIAGRAM

### SAA7824

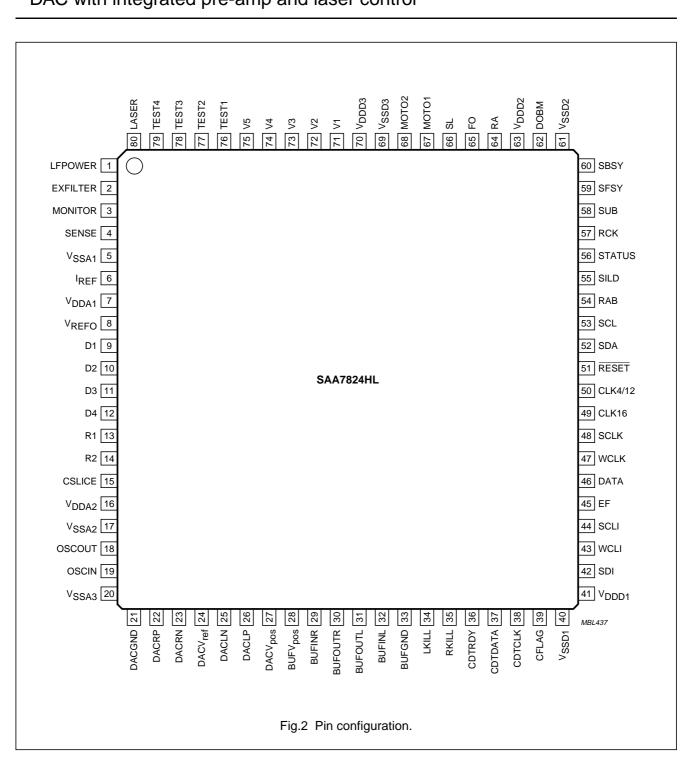

#### 6 PINNING

| SYMBOL              | PIN | I/O | DESCRIPTION                                                                  |

|---------------------|-----|-----|------------------------------------------------------------------------------|

| LFPOWER             | 1   | I   | laser power supply                                                           |

| EXFILTER            | 2   | 0   | 10 nF capacitor for laser start-up control                                   |

| MONITOR             | 3   | I   | laser monitor diode                                                          |

| SENSE               | 4   | I   | OPU ground reference point for MONITOR measurement                           |

| V <sub>SSA1</sub>   | 5   | SUP | analog ground 1                                                              |

| I <sub>REF</sub>    | 6   | 0   | reference current output (24 k $\Omega$ resistor connected to analog ground) |

| V <sub>DDA1</sub>   | 7   | SUP | analog supply voltage 1                                                      |

| V <sub>REFO</sub>   | 8   | I/O | servo reference voltage                                                      |

| D1                  | 9   | I   | diode voltage/current input (central diode signal input)                     |

| D2                  | 10  | I   | diode voltage/current input (central diode signal input)                     |

| D3                  | 11  | I   | diode voltage/current input (central diode signal input)                     |

| D4                  | 12  | I   | diode voltage/current input (central diode signal input)                     |

| R1                  | 13  | I   | diode voltage/current input (satellite diode signal input)                   |

| R2                  | 14  | I   | diode voltage/current input (satellite diode signal input)                   |

| CSLICE              | 15  | I/O | 10 nF capacitor for adaptive HF data slicer                                  |

| V <sub>DDA2</sub>   | 16  | SUP | analog supply voltage 2                                                      |

| V <sub>SSA2</sub>   | 17  | SUP | analog ground 2                                                              |

| OSCOUT              | 18  | 0   | crystal/resonator output                                                     |

| OSCIN               | 19  | I   | crystal/resonator input                                                      |

| V <sub>SSA3</sub>   | 20  | SUP | analog ground 3                                                              |

| DACGND              | 21  | I   | audio DAC ground                                                             |

| DACRP               | 22  | 0   | audio DAC right channel differential positive output                         |

| DACRN               | 23  | 0   | audio DAC right channel differential negative output                         |

| DACV <sub>ref</sub> | 24  | I/O | audio DAC decoupling point (10 $\mu$ F or 100 nF to ground                   |

| DACLN               | 25  | 0   | audio DAC left channel differential negative output                          |

| DACLP               | 26  | 0   | audio DAC left channel differential positive output                          |

| DACV <sub>pos</sub> | 27  | I   | audio DAC positive supply voltage                                            |

| BUFV <sub>pos</sub> | 28  | I   | audio buffer positive supply voltage                                         |

| BUFINR              | 29  | I   | audio buffer right input                                                     |

| BUFOUTR             | 30  | 0   | audio buffer right output                                                    |

| BUFOUTL             | 31  | 0   | audio buffer left output                                                     |

| BUFINL              | 32  | I   | audio buffer left input                                                      |

| BUFGND              | 33  | I   | audio buffer ground                                                          |

| LKILL               | 34  | 0   | KILL output for left channel (configurable as open-drain)                    |

| RKILL               | 35  | 0   | KILL output for right channel (configurable as open-drain)                   |

| CDTRDY              | 36  | 0   | CD text output to microcontroller ready flag                                 |

| CDTDATA             | 37  | 0   | CD text output data to microcontroller                                       |

| CDTCLK              | 38  | Ι   | CD text microcontroller clock input                                          |

| CFLAG               | 39  | 0   | correction flag output (open-drain)                                          |

| V <sub>SSD1</sub>   | 40  | SUP | digital ground 1                                                             |

## SAA7824

| SYMBOL            | PIN | I/O | DESCRIPTION                                                                          |  |  |

|-------------------|-----|-----|--------------------------------------------------------------------------------------|--|--|

| V <sub>DDD1</sub> | 41  | SUP | digital supply voltage 1                                                             |  |  |

| SDI               | 42  | I   | serial data input (loopback)                                                         |  |  |

| WCLI              | 43  | I   | word clock input (loopback)                                                          |  |  |

| SCLI              | 44  | I   | serial bit clock input (loopback)                                                    |  |  |

| EF                | 45  | 0   | C2 error flag output                                                                 |  |  |

| DATA              | 46  | 0   | serial data output                                                                   |  |  |

| WCLK              | 47  | 0   | word clock output                                                                    |  |  |

| SCLK              | 48  | 0   | serial clock output                                                                  |  |  |

| CLK16             | 49  | 0   | 16 MHz clock output                                                                  |  |  |

| CLK4/12           | 50  | 0   | configurable 4 MHz or 12 MHz clock output                                            |  |  |

| RESET             | 51  | I   | power-on reset input (active LOW)                                                    |  |  |

| SDA               | 52  | I/O | microcontroller interface data input/output (open-drain)                             |  |  |

| SCL               | 53  | I   | microcontroller interface clock input                                                |  |  |

| RAB               | 54  | I   | microcontroller interface R/W and load control input (4-wire)                        |  |  |

| SILD              | 55  | l   | microcontroller interface R/W and load control input (4-wire)                        |  |  |

| STATUS            | 56  | 0   | servo interrupt request line/decoder status register/DC offset value readback output |  |  |

| RCK               | 57  | I   | subcode clock input                                                                  |  |  |

| SUB               | 58  | 0   | P to W subcode output                                                                |  |  |

| SFSY              | 59  | 0   | subcode frame sync output                                                            |  |  |

| SBSY              | 60  | 0   | subcode block sync output                                                            |  |  |

| V <sub>SSD2</sub> | 61  | SUP | digital ground 2                                                                     |  |  |

| DOBM              | 62  | 0   | bi-phase mark output (externally buffered)                                           |  |  |

| V <sub>DDD2</sub> | 63  | SUP | digital supply voltage 2                                                             |  |  |

| RA                | 64  | 0   | radial actuator output                                                               |  |  |

| FO                | 65  | 0   | focus actuator output                                                                |  |  |

| SL                | 66  | 0   | sledge actuator output                                                               |  |  |

| MOTO1             | 67  | 0   | motor output 1 output                                                                |  |  |

| MOTO2             | 68  | 0   | motor output 2 output                                                                |  |  |

| V <sub>SSD3</sub> | 69  | SUP | digital ground 3                                                                     |  |  |

| V <sub>DDD3</sub> | 70  | SUP | digital supply voltage 3                                                             |  |  |

| V1                | 71  | I   | versatile pin 1 input                                                                |  |  |

| V2                | 72  | I   | versatile pin 2 input                                                                |  |  |

| V3                | 73  | 0   | versatile pin 3 output                                                               |  |  |

| V4                | 74  | 0   | versatile pin 4 output                                                               |  |  |

| V5                | 75  | 0   | versatile pin 5 output                                                               |  |  |

| TEST1             | 76  | I   | test pin 1 input                                                                     |  |  |

| TEST2             | 77  | I   | test pin 2 input                                                                     |  |  |

| TEST3             | 78  | I   | test pin 3 input                                                                     |  |  |

| TEST4             | 79  | I   | test pin 4 input                                                                     |  |  |

| LASER             | 80  | 0   | laser drive output                                                                   |  |  |

SAA7824

CD audio decoder, digital servo and filterless DAC with integrated pre-amp and laser control

SAA7824

#### 7 FUNCTIONAL DESCRIPTION

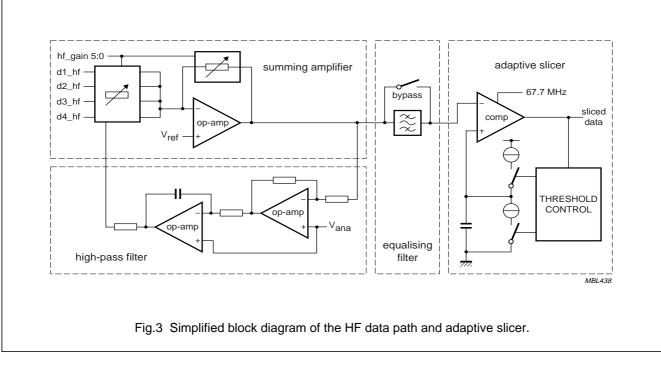

#### 7.1 Data acquisition and HF data path

The SAA7824 removes the need for an external diode signal pre-amplifier.

A simplified diagram of the HF data path is illustrated in Fig.3. The high-pass filter, equalizing filter HF gain and adaptive slicer are all register programmable, thus enabling the SAA7824 to be optimized for the intended application.

### 7.2 Decoder part

7.2.1 PRINCIPLE OPERATING MODES OF THE DECODER

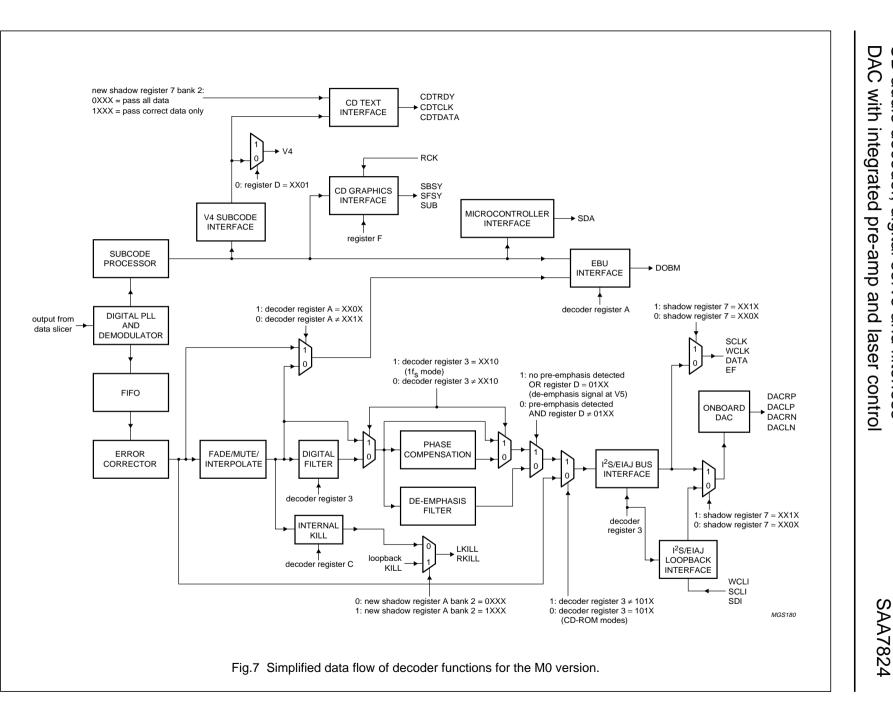

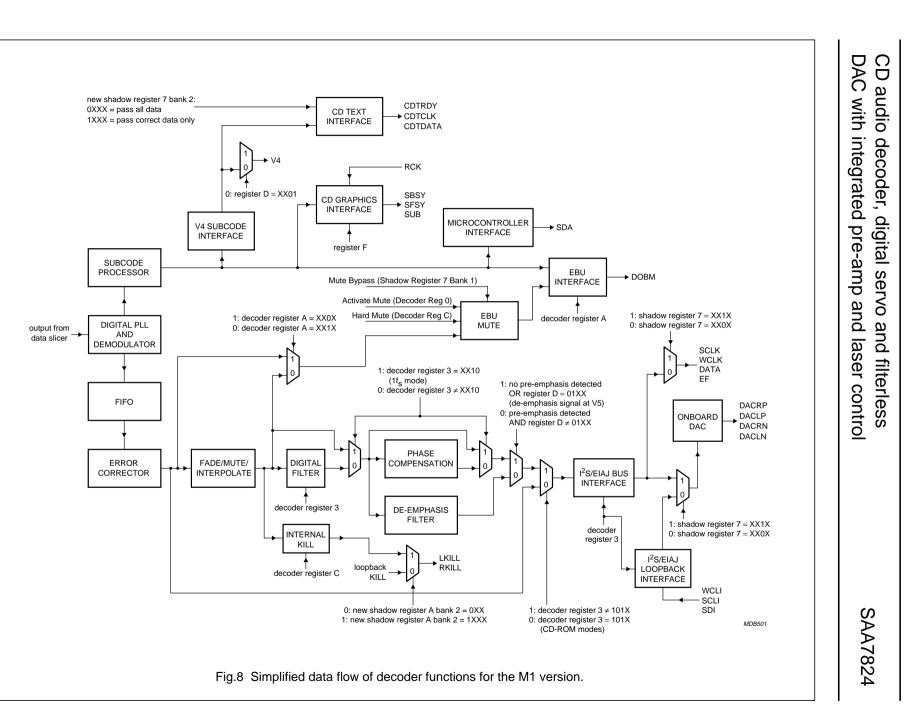

The decoding part supports a full audio specification and can operate at single-speed (n = 1), double-speed (n = 2) and quad-speed (n = 4). The factor 'n' is called the overspeed factor. A simplified data flow through the decoder part is illustrated in Fig.7 for the M0 version and Fig.8 for the M1 version.

#### 7.2.2 DECODER SPEED AND CRYSTAL FREQUENCY

The SAA7824 is a  $1\times$ ,  $2\times$  and  $4\times$  (three-speed) decoding device, with an internal Phase-Locked Loop (PLL) clock multiplier. Table 1 gives the playback speeds that are achievable in conjunction with crystal frequency, mechanism, and internal clock settings (selectable via decoder register B).

#### 7.2.3 LOCK-TO-DISC MODE

For electronic shock absorption applications, the SAA7824 can be put into lock-to-disc mode. This allows Constant Angular Velocity (CAV) disc playback with varying input data rates from the inside-to-outside of the disc.

In the lock-to-disc mode, the FIFO is blocked and the decoder will adjust its output data rate to the disc speed. Hence, the frequency of the I<sup>2</sup>S-bus (WCLK and SCLK) clocks are dependent on the disc speed. In the lock-to-disc mode there is a limit on the maximum variation in disc speed that the SAA7824 will follow. Disc speeds must always be within 25% to 100% range of their nominal value. The lock-to-disc mode is enabled or disabled by decoder register E.

### SAA7824

#### 7.2.4 STANDBY MODES

The SAA7824 may be placed in two standby modes, selected by decoder register B (it should be noted that the device core is still active):

- Standby 1: CD STOP mode; most I/O functions are switched off

- Standby 2: CD PAUSE mode; audio output features are switched off, but the motor loop, the motor output and the subcode interfaces remain active; this is also called a 'Hot Pause'.

In the standby modes the various pins will have the following values:

- MOTO1 and MOTO2: put in to high-impedance, PWM mode (Standby 1 and RESET: operating in Standby 2); put in high-impedance, PDM mode (Standby 1 and RESET: operating in Standby 2)

- Pins SCL and SDA: no interaction; normal operation continues

- Pins SCLK, WCLK, DATA, EF and DOBM: 3-state in both standby modes; normal operation continues after reset

- Pins OSCIN, OSCOUT, CLK16 and CLK4/12: no interaction; normal operation continues

- Pins V1 to V5 and CFLAG: no interaction; normal operation continues.

#### Table 1Playback speeds

| REGISTER B | REGISTER E | f <sub>xtal</sub> = 8.4672 MHz |

|------------|------------|--------------------------------|

| 0XXX       | 0XXX       | n = 1                          |

| 1XXX       | 0XXX       | n = 2; voltage mode<br>only    |

| 0XXX       | 1XXX       | n = 4; voltage mode<br>only    |

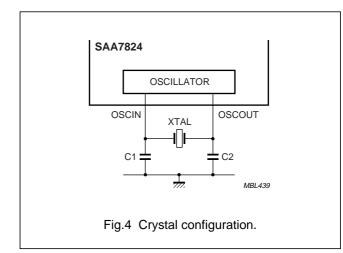

#### 7.3 Crystal oscillator

The crystal oscillator is a conventional 2-pin design which can also operate with ceramic resonators. The external components used around the crystal are illustrated in Fig.4 together with component values (C1 and C2) for a given crystal type given in Table 2. Oscillator frequencies that is used with the SAA7824 is 8.4672 MHz.

#### Table 2 External capacitor selection based upon the crystal type

| CRYSTAL LOAD<br>CAPACITANCE (C <sub>L</sub> ) | MAXIMUM SERIES<br>CRYSTAL RESISTANCE<br>(R <sub>S</sub> ) | EXTERNAL LOA | D CAPACITORS |

|-----------------------------------------------|-----------------------------------------------------------|--------------|--------------|

|                                               | 8 MHz                                                     | C1           | C2           |

| 10 pF                                         | <300 Ω                                                    | 8 pF         | 8 pF         |

| 20 pF                                         | <300 Ω                                                    | 27 pF        | 27 pF        |

| 30 pF                                         | <300 Ω                                                    | 47 pF        | 47 pF        |

#### 7.4 Data slicer and bit clock regenerator

The SAA7824 has an integrated adaptive data slicer which is clocked at 67 MHz. The slice level is controlled by internal current sources which are switched onto and integrated by the external capacitor connected to the CSLICE pin. The currents are switched under the control of a Digital Phase-Locked loop (DPLL).

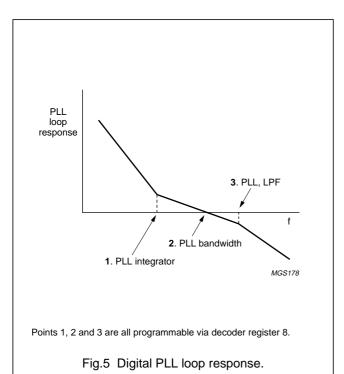

Regeneration of the bit clock is achieved with an internal fully digital PLL. No external components are required and the bit clock is not output. The PLL has two registers (8 and 9) for selecting bandwidth and equalization. The PLL loop response is illustrated in Fig.5.

For certain applications an off-track input is necessary. This is internally connected from the servo part (its polarity can be changed by the foc\_parm1 parameter), but may be input via pin V1 if selected by register C. If this flag is HIGH, the SAA7824 will assume that its servo part is following the wrong track, and will flag all incoming HF data as incorrect.

#### 7.5 DC offset cancellation

Unwanted DC offsets can exist within the photo-diode signals and are defined as the DC present in the system when the laser diode is switched off. They arise from various sources of imperfection within the system such as leakage in the photo diodes and offsets in the Optical Pick-Up (OPU) circuitry. The SAA7824 is capable of measuring these offsets and minimizing them.

#### 7.5.1 OFFSET CANCELLATION

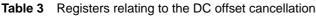

A number of registers are associated with the DC offset cancellation function; these registers are given in Table 3.

The measurement time of the DC offset is regulated by new shadow register C (bank 2). A longer time will yield more accurate results but will result in greater measurement durations.

New shadow register 3 (bank 3) is used to select which diode is to be measured.

#### 7.5.2 READING BACK THE DC OFFSET VALUE

The microcontroller needs to be able to read the DC offset measurements in order to calculate the correct cancellation value [for writing back to new shadow register 7 (bank 3)].

This is achieved by using the STATUS pin and setting decoder register 7 to XX10. Shadow register C (bank 3) can then be used to control the STATUS pin output; the register settings are given in Table 20.

Once the measurement time has been set and the diode selected, the STATUS pin should be set to read the DC offset ready flag [new shadow register C (bank 3) = X01X]. This signal will toggle HIGH after the prescribed measurement time. Changing the diode selection will result in the measurement timer being automatically reset.

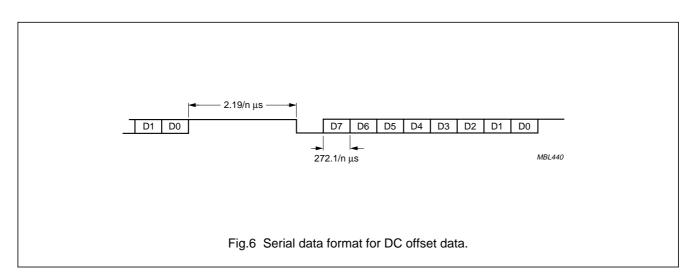

The microcontroller can read back the measurement by setting the STATUS pin to output the DC offset value [new shadow register C (bank 3) = X10X].

The offset value is repeatedly streamed out through the STATUS pin and is UART compatible. It should be noted that the MSB is inverted and will require re-inverting after the offset value has been captured. Timing information for this signal is illustrated in Fig.6.

The final DC cancellation value (as calculated by the microcontroller) can then be written to new shadow register 7 (bank 3). This is a multiple write register containing the cancellation values for all six diodes.

SAA7824

## CD audio decoder, digital servo and filterless DAC with integrated pre-amp and laser control

#### SHADOW SHADEN BITS ADDRESS INITIAL DATA **FUNCTION** REGISTER 10 С 1100 XX00 settling time = $354 \ \mu s$ reset (bank 2) DC offset XX01 settling time = 1 ms \_ measurement XX10 settling time = 2 ms \_ times XX11 settling time = 10 ms \_ 3 11 0011 0000 select D1 reset (bank 3) diode selection 0001 select D1 \_ for DC offset 0010 select D2 \_ measurement 0011 select D3 0100 select D4 \_ 0101 select R1 \_ 0110 select R2 \_ 0111 select D1 \_ 1100 С X00X STATUS pin outputs reset STATUS pin decoder status register control information X01X STATUS pin outputs DC \_ offset ready flag X10X STATUS pin outputs DC \_ offset value multi-write 0111 DC cancellation values for 7 DC cancellation $(9 \times 4 \text{ bits})$ diodes D1 to D4 and R1 levels and R2; see Table 20

Philips Semiconductors

CD audio decoder,

digital servo

and filterless

Product specification

ώ

2003 Oct 01

\_

Philips Semiconductors

Product specification

4

2003 Oct 01

\_

#### 7.6 Demodulator

#### 7.6.1 FRAME SYNC PROTECTION

A double timing system is used to protect the demodulator from erroneous sync patterns in the serial data. The master counter is only reset if:

- A sync coincidence is detected; sync pattern occurs 588 ±1 EFM clocks after the previous sync pattern

- A new sync pattern is detected within ±6 EFM clocks of its expected position.

The sync coincidence signal is also used to generate the PLL lock signal, which is active HIGH after 1 sync coincidence is found, and reset LOW if during 61 consecutive frames no sync coincidence is found. The PLL lock signal can be accessed via the SDA or STATUS pins selected by decoder registers 2, 7 and new shadow register C (bank 3).

Also incorporated in the demodulator is a Run Length 2 (RL2) correction circuit. Every symbol detected as RL2 will be pushed back to RL3. To do this, the phase error of both edges of the RL2 symbol are compared and the correction is executed at the side with the highest error probability.

#### 7.6.2 EFM DEMODULATION

The 14-bit EFM data and subcode words are decoded into 8-bit symbols.

#### 7.7 Subcode data processing

#### 7.7.1 Q-CHANNEL PROCESSING

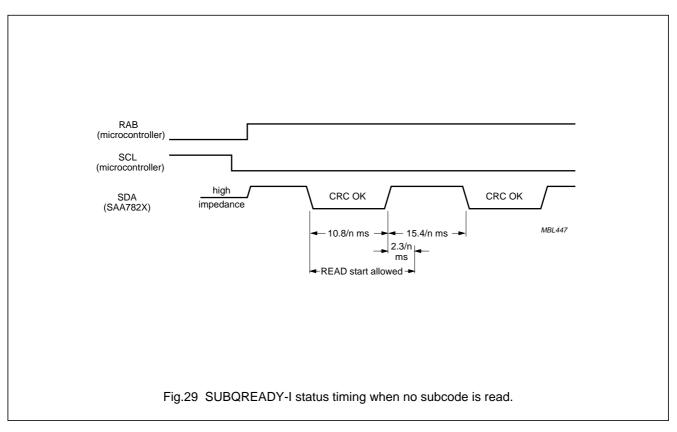

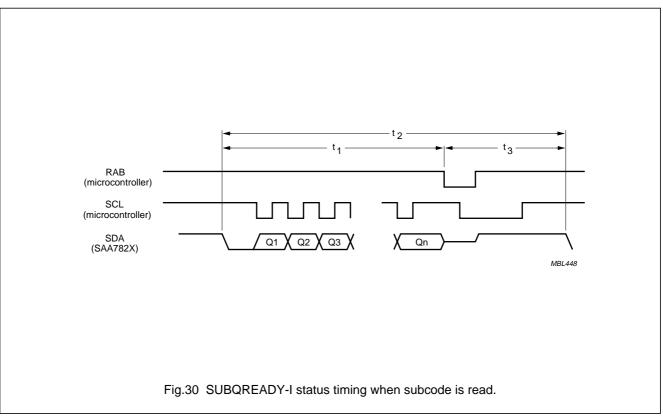

The 96-bit Q-channel word is accumulated in an internal buffer. The last 16 bits are used internally to perform a Cyclic Redundancy Check (CRC). If the data is good, the SUBQREADY-I signal will go LOW. SUBQREADY-I can be read via the SDA or STATUS pins, selected via decoder registers 2, 7 and new shadow register C (bank 3). Good Q-channel data may be read from pin SDA.

#### 7.7.2 EIAJ 3 AND 4-WIRE SUBCODE (CD GRAPHICS) INTERFACE

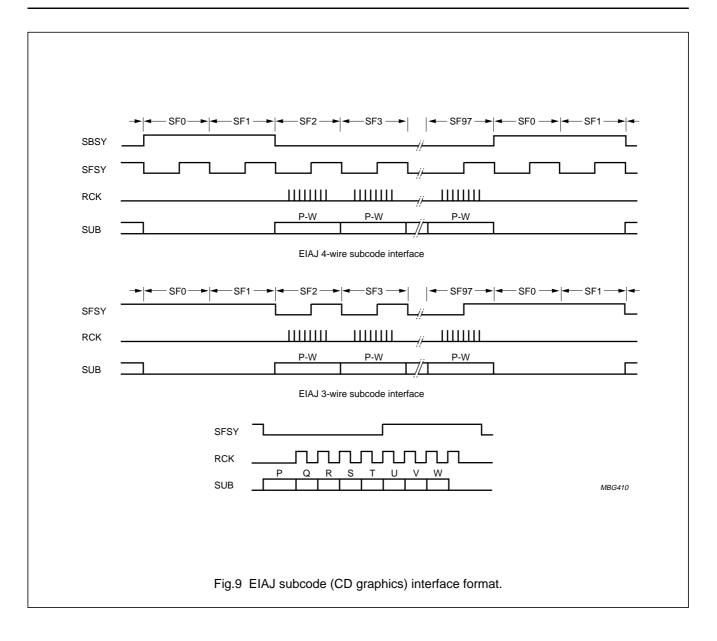

Data from all the subcode channels (P-to-W) may be read via the subcode interface, which conforms to EIAJ CP-2401. The interface is enabled and configured as either a 3 or 4-wire interface via decoder register F.

The subcode interface output formats are illustrated in Fig.9, where the RCK signal is supplied by another device such as a CD graphics decoder.

#### 7.7.3 V4 SUBCODE INTERFACE

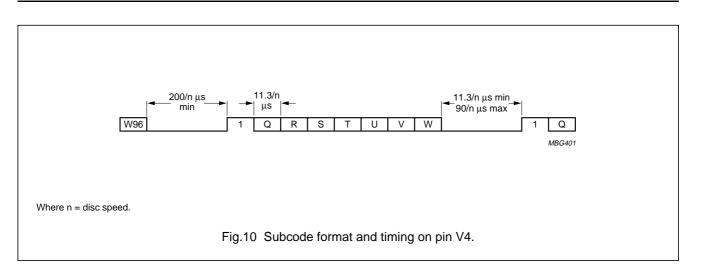

Data of subcode channels, Q-to-W, may be read via pin V4 if selected via decoder register D. The format is similar to RS232 and is illustrated in Fig.10. The subcode sync word is formed by a pause of (200/n)  $\mu$ s minimum. Each subcode byte starts with a logic 1 followed by 7 bits (Q-to-W). The gap between bytes is variable between (11.3/n)  $\mu$ s and (90/n)  $\mu$ s.

The subcode data is also available in the EBU output (DOBM) in a similar format.

#### 7.7.4 CD TEXT INTERFACE

R-to-W subcode data is captured and stored until a complete CD text PACK is formed. The least significant 16 bits of the PACK are used for a CRC.

The behaviour of the CD text interface is controlled by new shadow register 7 (bank 2). The interface can either flag all data (i.e. passed or failed CRC) or it can flag good data only.

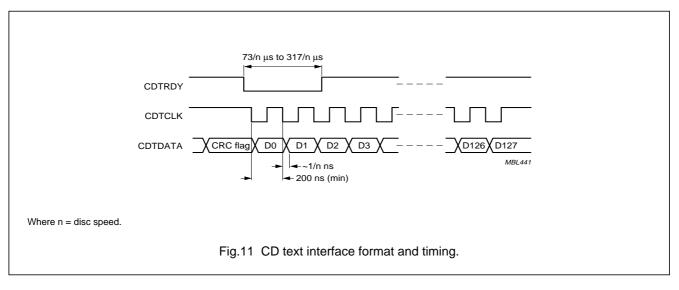

The data ready flag is monitored via pin CDTRDY and is active LOW. The pulse width varies from 73/n  $\mu$ s, for the first three packs, to 317/n  $\mu$ s for the fourth pack.

When a PACK becomes available, the initial value of the CDTDATA pin indicates the CRC result (HIGH = passed; LOW = failed). The microcontroller can fetch the data by applying a clock signal (maximum frequency = 5 MHz) to pin CDTCLK and reading the subsequent bitstream on pin CDTDATA.

The 128 data bits are streamed out LSB first. A complete CD text PACK consists of 4 header bytes, 12 data bytes, and 2 CRC bytes although the latter 2 bytes are dropped internally once the CRC calculation is complete. Please refer to the *"Red Book"* for further details relating to the format of a CD text PACK

The timing diagram for the CD text interface is illustrated in Fig.11.

### SAA7824

### SAA7824

#### 7.8 FIFO and error correction

The SAA7824 has a  $\pm 8$  frame FIFO. The error corrector is a t = 2, e = 4 type, with error corrections on both C1 (32 symbol) and C2 (28 symbol) frames. Four symbols are used from each frame as parity symbols. This error corrector can correct up to two errors on the C1 level and up to four errors on the C2 level.

The error corrector also contains a flag processor. Flags are assigned to symbols when the error corrector cannot ascertain if the symbols are definitely good. C1 generates output flags which are read after de-interleaving by C2, to help in the generation of C2 output flags.

The C2 output flags are used by the interpolator for concealment of uncorrectable errors. They are also output via the EBU signal (DOBM). The EF output will flag bytes in error in both audio and CD-ROM modes.

#### 7.8.1 FLAGS OUTPUT (CFLG)

The flags output pin CFLG shows the status of the error corrector and interpolator and is updated every frame (7.35  $\times$  n kHz). In the SAA7824, 8  $\times$  1-bit flags are present on the CFLG pin as illustrated in Fig.12. This signal shows the status of the error corrector and interpolator.

The first flag bit, F1, is the absolute time sync signal, the FIFO-passed subcode sync and relates the position of the subcode sync to the audio data (DAC output). This flag may also be used in a super FIFO or in the synchronization of different players. The output flags can be made available at bit 4 of the EBU data format (LSB of the 24-bit data word), if selected by decoder register A.

##

|    | 0 0.00 0. | - nage |    |    | _  | _  |    |                                                  |

|----|-----------|--------|----|----|----|----|----|--------------------------------------------------|

| F1 | F2        | F3     | F4 | F5 | F6 | F7 | F8 | DESCRIPTION                                      |

| 0  | Х         | Х      | Х  | Х  | Х  | X  | Х  | no absolute time sync                            |

| 1  | Х         | Х      | Х  | Х  | Х  | Х  | Х  | absolute time sync                               |

| Х  | 0         | 0      | Х  | Х  | Х  | X  | Х  | C1 frame contained no errors                     |

| Х  | 0         | 1      | Х  | Х  | Х  | X  | Х  | C1 frame contained 1 error                       |

| Х  | 1         | 0      | Х  | Х  | Х  | X  | Х  | C1 frame contained 2 errors                      |

| Х  | 1         | 1      | Х  | Х  | Х  | X  | Х  | C1 frame uncorrectable                           |

| Х  | Х         | Х      | 0  | 0  | Х  | X  | 0  | C2 frame contained no errors                     |

| Х  | Х         | Х      | 0  | 0  | Х  | Х  | 1  | C2 frame contained 1 error                       |

| Х  | Х         | Х      | 0  | 1  | Х  | X  | 0  | C2 frame contained 2 errors                      |

| Х  | Х         | Х      | 0  | 1  | Х  | X  | 1  | C2 frame contained 3 errors                      |

| Х  | Х         | Х      | 1  | 0  | Х  | X  | 0  | C2 frame contained 4 errors                      |

| Х  | Х         | Х      | 1  | 1  | X  | X  | 1  | C2 frame uncorrectable                           |

| Х  | Х         | Х      | Х  | Х  | 0  | 0  | Х  | no interpolations                                |

| Х  | Х         | Х      | Х  | Х  | 0  | 1  | Х  | at least one 1-sample interpolation              |

| Х  | Х         | Х      | Х  | Х  | 1  | 0  | Х  | at least one hold and no interpolations          |

| Х  | Х         | Х      | Х  | Х  | 1  | 1  | Х  | at least one hold and one 1-sample interpolation |

|    |           |        |    |    |    |    |    |                                                  |

#### Table 4 Output flags

#### 7.9 Audio functions

#### 7.9.1 DE-EMPHASIS AND PHASE LINEARITY

When pre-emphasis is detected in the Q-channel subcode, the digital filter automatically includes a de-emphasis filter section. When de-emphasis is not required, a phase compensation filter section controls the phase of the digital oversampling filter to  $\leq \pm 1^{\circ}$  within the band 0 to 16 kHz. With de-emphasis the filter is not phase linear.

If the de-emphasis signal is set to be available at pin V5, selected via decoder register D, then the de-emphasis filter is bypassed.

#### 7.9.2 DIGITAL OVERSAMPLING FILTER

For optimizing performance with an external DAC, the SAA7824 contains a 2 to 4 times oversampling IIR filter. The filter specification of the 4 times oversampling filter is given in Table 5.

These attenuations do not include the sample-and-hold at the external DAC output or the DAC post filter. When using the oversampling filter, the output level is scaled -0.5 dB down to avoid overflow on full-scale sine wave inputs (0 to 20 kHz).

| PASS BAND    | STOP BAND    | ATTENUATION |

|--------------|--------------|-------------|

| 0 to 9 kHz   | —            | ≤0.001 dB   |

| 19 to 20 kHz | —            | ≤0.03 dB    |

| _            | 24 kHz       | ≥25 dB      |

| _            | 24 to 27 kHz | ≥38 dB      |

| -            | 27 to 35 kHz | ≥40 dB      |

| _            | 35 to 64 kHz | ≥50 dB      |

| _            | 64 to 68 kHz | ≥31 dB      |

| _            | 68 kHz       | ≥35 dB      |

| _            | 69 to 88 kHz | ≥40 dB      |

#### Table 5 Filter specification

#### 7.9.3 CONCEALMENT

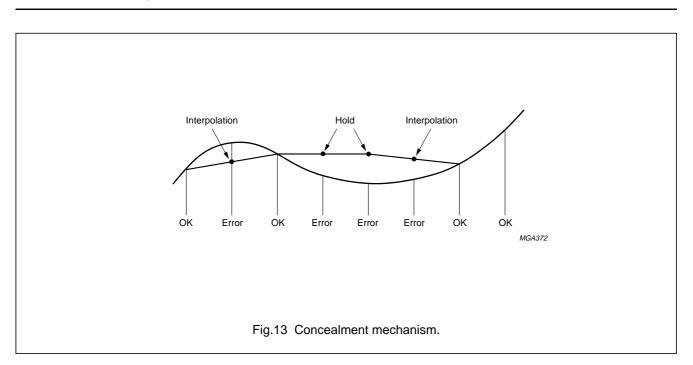

A 1-sample linear interpolator becomes active if a single sample is flagged as erroneous but cannot be corrected. The erroneous sample is replaced by a level midway between the preceding and following samples. Left and right channels have independent interpolators. If more than one consecutive non-correctable sample is found, the last good sample is held. A 1-sample linear interpolation is then performed before the next good sample; see Fig.13.

In CD-ROM modes (i.e. the external DAC interface is selected to be in a CD-ROM format) concealment is not executed.

#### 7.9.4 MUTE, FULL-SCALE, ATTENUATION AND FADE

A digital level controller is present on the SAA7824 which performs the functions of soft mute, full-scale, attenuation and fade; these are selected via decoder register 0:

- Mute: signal reduced to 0 in a maximum of 128 steps; 3/n ms

- Attenuation: signal scaled by –12 dB

- Full-scale: ramp signal back to 0 dB level; from mute it takes 3/n ms

- Fade: activates a 128 stage counter which allows the signal to be scaled up or down in 0.07 dB steps

- 128 = full-scale

- 120 = -0.5 dB (i.e. full-scale if oversampling filter is used)

- − 32 = −12 dB

- 0 = mute.

#### 7.9.5 PEAK DETECTOR

The peak detector measures the highest audio level (absolute value) on positive peaks for left and right channels. The 8 most significant bits are output in the Q-channel data in place of the CRC bits. Bits 81 to 88 contain the left peak value (bit 88 = MSB) and bits 89 to 96 contain the right peak value (bit 96 = MSB). The values are reset after reading Q-channel data via pin SDA.

#### 7.10 Audio DAC interface

7.10.1 INTERNAL DYNAMIC ELEMENT MATCHING DIGITAL-TO-ANALOG CONVERTER

The onboard audio DEM DAC operates at an oversampling rate of  $96f_s$  and is designed for operation with an audio input at  $1f_s$ . The DAC is equipped with two pairs of stereo outputs for driving medium impedance line outputs and for directly driving low impedance headphones. A pair of analog inputs are provided to enable external audio sources to make use of the headphone output buffers.

Audio data from the decoder part of the SAA7824 can be routed as described in Sections 7.10.1.1 and 7.10.1.2.

| SHADEN BITS    | SHADOW<br>REGISTER             | ADDRESS | DATA | FUNCTION                                                                         | RESET |

|----------------|--------------------------------|---------|------|----------------------------------------------------------------------------------|-------|

| 01<br>(bank 1) | 7<br>control of<br>onboard DAC | 0111    | 0000 | use external DAC or route audio data<br>back into onboard DAC (loopback<br>mode) | reset |

|                |                                |         | 0010 | route audio data directly into onboard DAC (non-loopback mode)                   | _     |

#### Table 6 Shadow register

#### 7.10.1.1 Use of internal DAC

Setting shadow register 7 to 0010 will route audio data from the decoder into the internal DAC. To enable the on-board DAC, the DAC interface format (set by register 3) must be set to 16-bit  $1f_s$  mode, either I<sup>2</sup>S-bus or EIAJ format. CD-ROM mode can also be used if interpolation is not required. The serial data output pins for interfacing with an external DAC (SCLK, WCLK, DATA and EF) are set to high-impedance.

SAA7824

#### 7.10.1.2 Loopback external data into onboard DAC

The onboard DAC can also be set to accept serial data inputs from an external source, e.g. an Electronic Shock Absorption (ESA) IC. This is known as loopback mode and is enabled by setting shadow register 7 to 0000. This enables the serial data output pins (SCLK, WCLK, DATA and EF) so that data can be routed from the SAA7824 to an external ESA system (or external DAC).

The serial data from an external ESA IC can then also be input to the onboard DAC on the SAA7824 by utilising the serial data input interface (SCLI, SDI and WCLI).

In this mode, a wide range of data formats to the external ESA IC can be programmed as shown in Table 7. However, the serial input on the SAA7824 will always expect the input data from the ESA IC to be 16-bit  $1f_s$  and the same data format, either I<sup>2</sup>S-bus or EIAJ, as the serial output format (set by decoder register 3).

#### 7.10.2 EXTERNAL DAC INTERFACE

Audio data from the SAA7824 can be sent to an external DAC, identical to the SAA732x series, in 'loopback' mode (i.e. shadow register 7 is set to 0000).

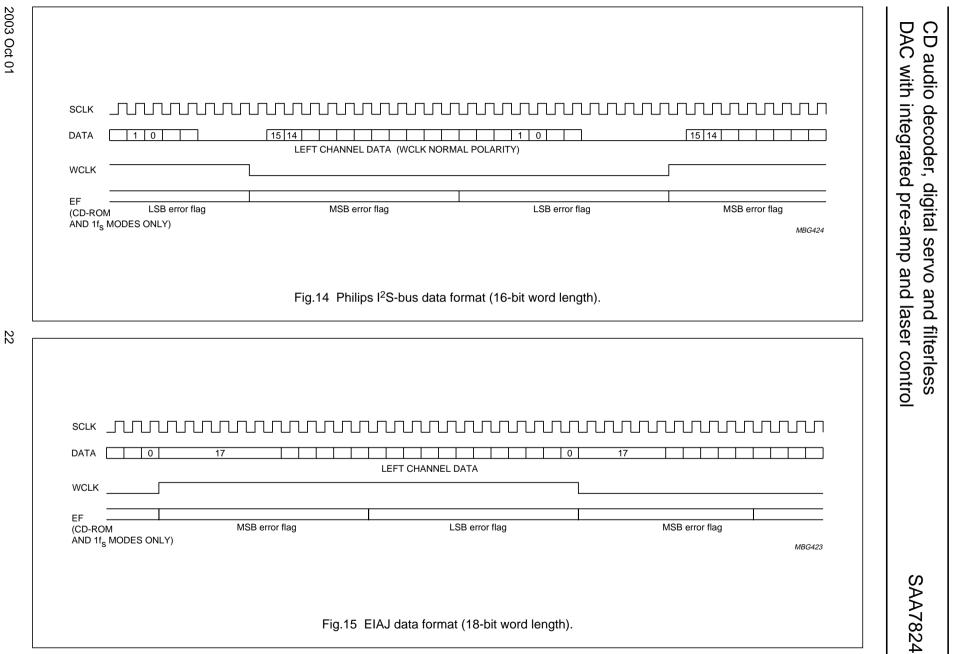

The SAA7824 is compatible with a wide range of external DACs. Eleven formats are supported and are given in Table 7. Figures 14 and 15 show the Philips I<sup>2</sup>S-bus and the EIAJ data formats respectively. When the decoder is operated in lock-to-disc mode, the SCLK frequency is dependent on the disc speed factor 'd'.

All formats are MSB first and  $1f_s$  is 44.1 kHz. The polarity of the WCLK and the data can be inverted; selectable by decoder register 7. It should be noted that EF is only a defined output in CD-ROM and  $1f_s$  modes.

When using an external DAC (or when using the onboard DAC in non-loopback mode), the serial data inputs to the onboard DAC (SCLI, SDI and WCLI) should be tied to ground.

| REGISTER 3 | SAMPLE<br>FREQUENCY | NUMBER OF<br>BITS    | SCLK (MHz) | FORMAT                                                    | INTERPOLATION |

|------------|---------------------|----------------------|------------|-----------------------------------------------------------|---------------|

| 1010       | f <sub>s</sub>      | 16                   | 2.1168 × n | CD-ROM<br>(I <sup>2</sup> S-bus)                          | no            |

| 1011       | f <sub>s</sub>      | 16                   | 2.1168 × n | CD-ROM (EIAJ)                                             | no            |

| 1110       | f <sub>s</sub>      | 16/18 <sup>(1)</sup> | 2.1168 × n | Philips I <sup>2</sup> S-bus<br>16/18 bits <sup>(1)</sup> | yes           |

| 0010       | f <sub>s</sub>      | 16                   | 2.1168 × n | EIAJ 16 bits                                              | yes           |

| 0110       | f <sub>s</sub>      | 18                   | 2.1168 × n | EIAJ 18 bits                                              | yes           |

| 0000       | 4f <sub>s</sub>     | 16                   | 8.4672 × n | EIAJ 16 bits                                              | yes           |

| 0100       | 4f <sub>s</sub>     | 18                   | 8.4672 × n | EIAJ 18 bits                                              | yes           |

| 1100       | 4f <sub>s</sub>     | 18                   | 8.4672 × n | Philips I <sup>2</sup> S-bus<br>18 bits                   | yes           |

| 0011       | 2f <sub>s</sub>     | 16                   | 4.2336 × n | EIAJ 16 bits                                              | yes           |

| 0111       | 2f <sub>s</sub>     | 18                   | 4.2336 × n | EIAJ 18 bits                                              | yes           |

| 1111       | 2fs                 | 18                   | 4.2336 × n | Philips I <sup>2</sup> S-bus<br>18 bits                   | yes           |

#### Table 7 DAC interface formats

#### Note

1. In this mode the first 16 bits contain data, but if any of the fade, attenuate or de-emphasis filter functions are activated then the first 18 bits contain data.

Product specification

Philips Semiconductors

#### Product specification

## CD audio decoder, digital servo and filterless DAC with integrated pre-amp and laser control

### SAA7824

#### 7.11 EBU interface

The bi-phase mark digital output signal at pin DOBM is in accordance with the format defined by the IEC 60958 specification. Three different modes can be selected via decoder register A:

- DOBM pin held LOW

- Data taken before concealment, mute and fade (must always be used for CD-ROM modes)

- Data taken after concealment, mute and fade.

An additional mute function is available via shadow register 7 (bank 1) and decoder register 0 and C. They provide the following:

- Hard mute: immediate mute of the audio sample in the ROM mode at 1×, 2× or 4×

- Soft mute: 3 ms ramp up or ramp down of the audio samples in the 1× audio mode

- Bypass: switches the EBU mute function out of the EBU signal path.

#### 7.11.1 FORMAT

The digital audio output consists of 32-bit words ('subframes') transmitted in bi-phase mark code (two transitions for a logic 1 and one transition for a logic 0). Words are transmitted in blocks of 384. The EBU frame format is given in Table 8.

| FUNCTION       | BITS    | DESCRIPTION                                                                      |  |

|----------------|---------|----------------------------------------------------------------------------------|--|

| Sync           | 0 to 3  | _                                                                                |  |

| Auxiliary      | 4 to 7  | not used; normally zero                                                          |  |

| Error flags    | 4       | CFLG error and interpolation flags when selected by register A                   |  |

| Audio sample   | 8 to 27 | first 4 bits not used (always zero); twos complement; LSB = bit 12, MSB = bit 27 |  |

| Validity flag  | 28      | valid = logic 0                                                                  |  |

| User data      | 29      | used for subcode data (Q-to-W)                                                   |  |

| Channel status | 30      | control bits and category code                                                   |  |

Table 8 EBU frame format; see also Table 9

### Table 9 Description of EBU frame function

| FUNCTION       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sync           | The sync word is formed by violation of the bi-phase rule and therefore does not contain any data.<br>Its length is equivalent to 4 data bits. The 3 different sync patterns indicate the following situations:<br>sync B; start of a block (384 words), word contains left sample; sync M; word contains left sample<br>(no block start) and sync W; word contains right sample. |

| Audio sample   | Left and right samples are transmitted alternately.                                                                                                                                                                                                                                                                                                                               |

| Validity flag  | Audio samples are flagged (bit 28 = 1) if an error has been detected but was uncorrectable. This flag remains the same even if data is taken after concealment.                                                                                                                                                                                                                   |

| User data      | Subcode bits Q-to-W from the subcode section are transmitted via the user data bit. This data is asynchronous with the block rate.                                                                                                                                                                                                                                                |

| Channel status | The channel status bit is the same for left and right words. Therefore a block of 384 words contains 192 channel status bits. The category code is always CD. The bit assignment is given in Table 10.                                                                                                                                                                            |

SAA7824

| FUNCTION       | BITS                     | DESCRIPTION                                                                                                                               |  |  |  |

|----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Control        | 0 to 3                   | copy of CRC checked Q-channel control bits 0 to 3; bit 2 is logic 1 when copy permitted; bit 3 is logic 1 when recording has pre-emphasis |  |  |  |

| Reserved mode  | 4 to 7                   | always zero                                                                                                                               |  |  |  |

| Category code  | 8 to 15                  | CD: bit 8 = logic 1, all other bits = logic 0                                                                                             |  |  |  |

| Clock accuracy | 28 to 29                 | set by register A; 10 = level I; 00 = level II; 01 = level III                                                                            |  |  |  |

| Remaining      | 6 to 27 and<br>30 to 191 | always zero                                                                                                                               |  |  |  |

#### Table 10 Bit assignment

#### 7.12 KILL features

#### 7.12.1 THE KILL CIRCUIT

The KILL circuit detects digital silence by testing for an all-zero or all-ones data word in the left and right channels. This occurs in two places; prior to the digital filter (internal KILL), and in the digital DAC (loopback/external KILL). Programming bit 3 of new shadow register A (bank 2) determines whether internal or external data is used. The output is switched to active HIGH when silence has been detected for at least 270 ms, or if mute is active, or in CD-ROM mode. Two KILL modes are available which can be selected by decoder register C:

- Mono KILL: LKILL and RKILL are both active HIGH when silence is detected on left and right channels simultaneously

- Stereo KILL: LKILL and RKILL are active HIGH independently of each other when silence is detected on either channel.

#### 7.12.2 SILENCE INJECTION

The silence inject function monitors the left and right KILL signals and forces the analog DAC into silence when KILL is asserted. This improves the internal Signal-to-Noise Ratio (SNR) by preventing any spurious noise from reaching the DAC. The silence inject function can be enabled or disabled by programming bit 2 of the new shadow register A (bank 2).

#### 7.13 Audio features off

The audio features can be turned off (selected by decoder register E) and will affect the following functions:

- Digital filter, fade, peak detector, internal KILL circuit (although RKILL and LKILL outputs still active) are disabled

- V5 (if selected to be the de-emphasis flag output) and the EBU outputs become undefined.

The EBU output should be set LOW prior to switching the audio features off and after switching the audio features back on, a full-scale command should be given.

#### 7.14 The versatile pins interface

The SAA7824 has five pins that can be reconfigured for different applications.

The functions of these versatile pins are identical to the SAA732x series and can be programmed by decoder registers C, D and shadow register 3 (bank 1) as shown in Table 11.

SAA7824

| PIN<br>NAME | PIN<br>NUMBER | TYPE   | REGISTER<br>ADDRESS | REGISTER<br>DATA | FUNCTION                                                                                         |  |

|-------------|---------------|--------|---------------------|------------------|--------------------------------------------------------------------------------------------------|--|

| V1          | 71            | input  | 1100                | XXX1             | external off-track signal input                                                                  |  |

|             |               |        | _                   | XXX0             | internal off-track signal used input may be read via decoder status bit; selected via register 2 |  |

| V2          | 72            | input  | _                   | -                | input may be read via decoder status bit;<br>selected via register 2                             |  |

| V3          | 73            | output | 1100                | 00XX             | output = 0                                                                                       |  |

|             |               |        | -                   | 01XX             | output = 1                                                                                       |  |

| V4          | 74            | output | 1101                | 0000             | 4-line motor drive (using V4 and V5)                                                             |  |

|             |               |        | _                   | XX01             | Q-to-W subcode output                                                                            |  |

|             |               |        | -                   | XX10             | output = 0                                                                                       |  |

|             |               |        | -                   | XX11             | output = 1                                                                                       |  |

| V5          | 75            | output | 1101                | 01XX             | de-emphasis output (active HIGH)                                                                 |  |

|             |               |        | -                   | 10XX             | output = 0                                                                                       |  |

|             |               |        | _                   | 11XX             | output = 1                                                                                       |  |

#### Table 11 Pin applications

#### 7.15 Spindle motor control

#### 7.15.1 MOTOR OUTPUT MODES

The spindle motor speed is controlled by a fully integrated digital servo. Address information from the internal  $\pm 8$  frame FIFO and disc speed information are used to calculate the motor control output signals. Several output modes, selected by decoder register 6, are supported:

- Pulse density, 2-line (true complement output),  $(1 \times n)$  MHz sample frequency

- PWM output, 2-line,  $(22.05 \times n)$  kHz modulation frequency

- PWM output, 4-line, (22.05  $\times$  n) kHz modulation frequency

- CDV motor mode.

#### 7.15.1.1 Pulse density output mode

In the pulse density mode the motor output pin (MOTO1) is the pulse density modulated motor output signal.

A 50% duty factor corresponds with the motor not actuated, higher duty factors mean acceleration, lower duty factors means braking. In this mode, the MOTO2 signal is the inverse of the MOTO1 signal. Both signals change state only on the edges of a  $(1 \times n)$  MHz internal clock signal.

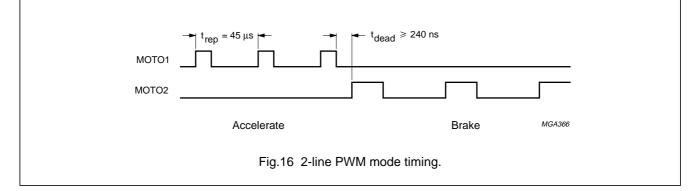

#### 7.15.1.2 PWM output mode (2-line)

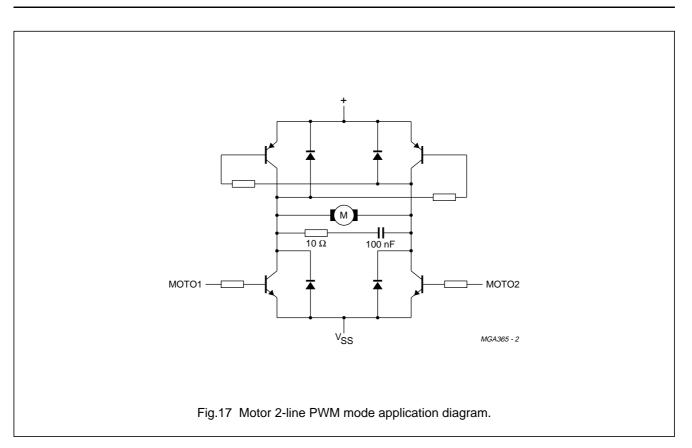

In the PWM mode the motor acceleration signal is put in pulse-width modulation form on the MOTO1 output. The motor braking signal is pulse-width modulated on the MOTO2 output. The timing is illustrated in Fig 16. A typical application diagram is illustrated in Fig 17.

SAA7824

## CD audio decoder, digital servo and filterless DAC with integrated pre-amp and laser control

#### 7.15.1.3 PWM output mode (4-line)

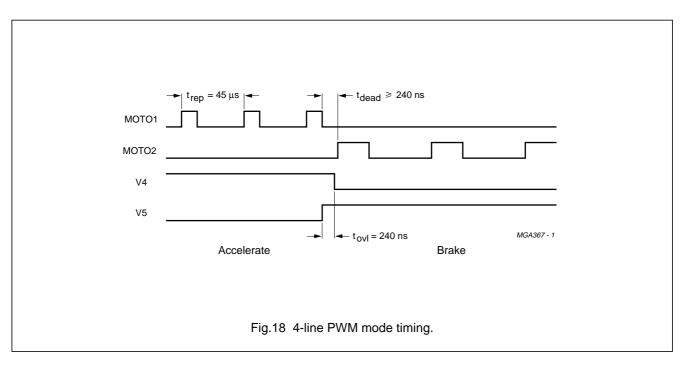

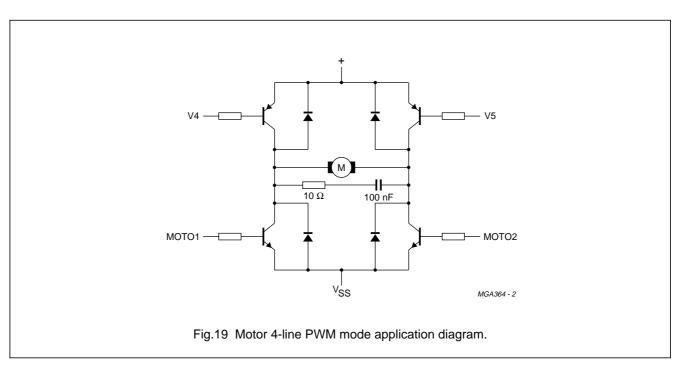

Using two extra outputs from the versatile pins interface, it is possible to use the SAA7824 with a 4-input motor bridge. The timing is illustrated in Fig 18. A typical application diagram is illustrated in Fig 19.

SAA7824

## CD audio decoder, digital servo and filterless DAC with integrated pre-amp and laser control

#### 7.15.1.4 CDV/CAV output mode

In the CDV motor mode, the FIFO position will be put in pulse-width modulated form on the MOTO1 pin [carrier frequency ( $300 \times d$ ) Hz], where 'd' is the disc speed factor. The PLL frequency signal will be put in pulse-density modulated form (carrier frequency  $4.23 \times n$  MHz) on the MOTO2 pin. The integrated motor servo is disabled in this mode.

The PWM signal on MOTO1 corresponds to a total memory space of 20 frames, therefore the nominal FIFO position (half full) will result in a PWM output of 60%.

In the lock-to-disc (CAV) mode the CDV motor mode is the only mode that can be used to control the motor.

#### 7.15.2 SPINDLE MOTOR OPERATING MODES

The operating modes of the motor servo are controlled by decoder register 1; see Table 12.

In the SAA7824 decoder there is an anti-windup mode for the motor servo, selected via decoder register 1. When the anti-windup mode is activated the motor servo integrator will hold if the motor output saturates.

#### 7.15.2.1 Motor OV flag

The SAA7824 contains a servo loop that is used to regulate the spindle speed. The motor OV flag is provided to indicate when the motor output has overloaded. During a large change in disc speed i.e. by a long jump or x-factor change, the motor OV flag will be asserted due to the full and longer duration required to attain the new desired speed.

The OV flag indicates when the internal processes of the modulator have overflowed and not necessarily when the output power has reached 100%. Similarly, the flag does not fall at a specific output power level but at a specific speed error level. The error level at which the flag falls is determined by the selected servo gain, and will be internally equivalent to  $+3 \times$  gain or  $-3 \times$  gain.

#### 7.15.2.2 Power limit

In start mode 1, start mode 2, stop mode 1 and stop mode 2, a fixed positive or negative voltage is applied to the motor.

This voltage can be programmed as a percentage of the maximum possible voltage, via register 6, to limit current drain during start and stop.

The following power limits are possible:

• 100% (no power limit), 75%, 50% or 37% of maximum.

#### Product specification

## CD audio decoder, digital servo and filterless DAC with integrated pre-amp and laser control

### SAA7824

#### 7.15.3 LOOP CHARACTERISTICS

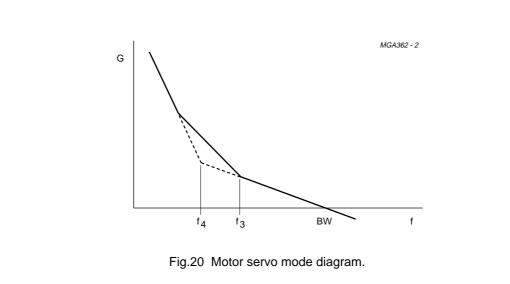

The gain and crossover frequencies of the motor control loop can be programmed via decoder registers 4 and 5. The following parameter values are possible:

- Gains: 3.2, 4.0, 6.4, 8.0, 12.8, 16, 25.6 and 32

- Crossover frequency  $f_4$ : 0.5 × n Hz, 0.7 × n Hz,  $1.4 \times n$  Hz and  $2.8 \times n$  Hz

- Crossover frequency  $f_3: 0.85 \times n$  Hz,  $1.71 \times n$  Hz and  $3.42 \times n$  Hz.

It should be noted that the crossover frequencies f3 and f4 are scaled with the overspeed factor 'n' whereas the gains are not.

#### 7.15.4 FIFO OVERFLOW

If FIFO overflow occurs during Play mode (e.g. as a result of motor rotational shock), the FIFO will be automatically reset to 50% and the audio interpolator will conceal as much as possible to minimize the effect of data loss.

- . . . . .

| MODE         | DESCRIPTION                                                                                                                                                                                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Start mode 1 | The disc is accelerated by applying a positive voltage to the spindle motor. No decisions are involved and the PLL is reset. No disc speed information is available for the microcontroller.                                                                                             |

| Start mode 2 | The disc is accelerated as in start mode 1, however the PLL will monitor the disc speed. When the disc reaches 75% of its nominal speed, the controller will switch to jump mode. The motor status signals selectable via register 2 are valid.                                          |

| Jump mode    | Motor servo enabled but FIFO kept reset at 50%, integrator is held. The audio is muted but it is possible to read the subcode. It should be noted that in the CD-ROM modes the data, on EBU and the I <sup>2</sup> S-bus, is not muted.                                                  |

| Jump mode 1  | Similar to jump mode but motor integrator is kept at zero. It is used for long jumps where there is a large change in disc speed.                                                                                                                                                        |

| Play mode    | FIFO released after resetting to 50% and the audio mute is released.                                                                                                                                                                                                                     |

| Stop mode 1  | Disc is braked by applying a negative voltage to the motor; no decisions are involved.                                                                                                                                                                                                   |

| Stop mode 2  | The disc is braked as in stop mode 1 but the PLL will monitor the disc speed. As soon as the disc reaches 12% (or 6%, depending on the programmed brake percentage, via register E) of its nominal speed, the MOTSTOP status signal will go HIGH and switch the motor servo to off mode. |

| Off mode     | Motor not steered.                                                                                                                                                                                                                                                                       |

#### 7.16 Servo part

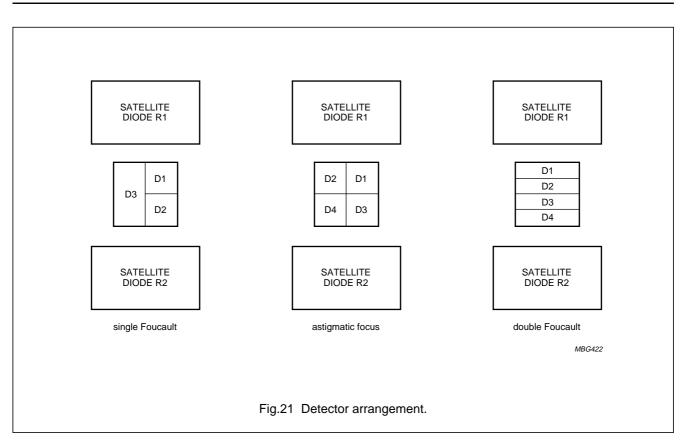

7.16.1 DIODE SIGNAL PROCESSING

The photo detector in conventional two-stage three-beam Compact Disc systems normally contains six discrete diodes. Four of these diodes (three for single foucault systems) carry the Central Aperture signal (CA) while the other two diodes (satellite diodes) carry the radial tracking information. The CA signals are summed into an HF signal for the decoder function and are also differentiated (after analog-to-digital conversion) to produce the low frequency focus control signals. The low frequency content of the six (five if single Foucault) photo diode inputs are converted to digital Pulse Density Modulated (PDM) bitstreams by six Sigma-delta ADCs. These support a range of OPUs by interfacing to Voltage mode mechanisms and by having 16 selectable gain ranges in two sets, one set for D1-to-D4 and the other for R1 and R2.

| Table 13 | Shadow r | egister | settings to | o control | diode | voltage | ranges |

|----------|----------|---------|-------------|-----------|-------|---------|--------|

|----------|----------|---------|-------------|-----------|-------|---------|--------|

| SHADEN BITS | SHADOW<br>REGISTER             | ADDRESS | DATA | VOLTAGE (mV) | INITIAL |

|-------------|--------------------------------|---------|------|--------------|---------|

| 01          | A                              | 1010    | 0000 | 20           | _       |

| (bank 1)    | signal magnitude               |         | 0001 | 25           | _       |

|             | control for diodes<br>D1 to D4 |         | 0010 | 30           | _       |

|             | (LF only)                      |         | 0011 | 40           | _       |

|             |                                |         | 0100 | 60           | _       |

|             |                                |         | 0101 | 75           | _       |

|             |                                |         | 0110 | 100          | _       |

|             |                                |         | 0111 | 120          | _       |

|             |                                |         | 1000 | 150          | _       |

|             |                                |         | 1001 | 200          | _       |

|             |                                |         | 1010 | 270          | _       |

|             |                                |         | 1011 | 350          | -       |

|             |                                |         | 1100 | 450          | _       |

|             |                                | -       | 1101 | 600          | _       |

|             |                                |         | 1110 | 720          | _       |

|             |                                |         | 1111 | 960          | reset   |

SAA7824

#### SHADOW SHADEN BITS ADDRESS DATA VOLTAGE (mV) INITIAL REGISTER 01 С 20 1100 0000 (bank 1) signal magnitude 0001 25 \_ control for diodes 0010 30 \_ R1 and R2 (LF 0011 40 only) 60 0100 \_ 0101 75 \_ 0110 100 0111 120 \_ 1000 150 1001 200 1010 270 \_ 1011 350 1100 450 \_ 1101 600 \_ 1110 720 1111 960 reset

### 7.16.2 SIGNAL CONDITIONING

The digital codes retrieved from the ADCs are applied to logic circuitry to obtain the various control signals. The signals from the central aperture diodes are processed to obtain a normalised focus error signal:

CD audio decoder, digital servo and filterless

DAC with integrated pre-amp and laser control

$$FE_n = \frac{D1 - D2}{D1 + D2} - \frac{D3 - D4}{D3 + D4}$$

Where the detector set-up is assumed to be as shown in Fig.21.

In the event of single Foucault focusing method, the signal conditioning can be switched under software control such that the signal processing is as follows:

$$FE_n = 2 \times \frac{D1 - D2}{D1 + D2}$$

The error signal, FE<sub>n</sub>, is further processed by a Proportional Integral and Differential (PID) filter section.

A Focus OK (FOK) flag is generated by the central aperture signal and an adjustable reference level. This signal is used to provide extra protection for the Track-Loss (TL) generation, the focus start-up procedure and the dropout detection.

The radial or tracking error signal is generated by the satellite detector signals R1 and R2. The radial error signal can be formulated as follows:

$RE_s = (R1 - R2) \times re_gain + (R1 + R2) \times re_offset.$

Where the index 's' indicates the automatic scaling operation which is performed on the radial error signal. This scaling is necessary to avoid non-optimum dynamic range usage in the digital representation and reduces the radial bandwidth spread. Furthermore, the radial error signal will be made free from offset during start-up of the disc.

The four signals from the central aperture detectors, together with the satellite detector signals generate a Track Position signal (TPI) which can be formulated as follows:

$TPI = sign [(D1 + D2 + D3 + D4) - (R1 + R2) \times sum_gain]$

Where the weighting factor sum\_gain is generated internally by the SAA7824 during initialization.

SAA7824

## CD audio decoder, digital servo and filterless DAC with integrated pre-amp and laser control

#### 7.16.3 FOCUS SERVO SYSTEM

#### 7.16.3.1 Focus start-up

Five initially loaded coefficients influence the start-up behaviour of the focus controller. The automatically generated triangular voltage can be influenced by 3 parameters; for height (ramp\_height) and DC offset (ramp\_offset) of the triangle and its steepness (ramp\_incr).

For protection against false focus point detections two parameters are available which are an absolute level on the CA signal (CA\_start) and a level on the FE<sub>n</sub> signal (FE\_start). When this CA level is reached the FOK signal becomes true.

If the FOK signal is true and the level on the  $FE_n$  signal is reached, the focus PID is enabled to switch-on when the next zero crossing is detected in the  $FE_n$  signal.

#### 7.16.3.2 Focus position control loop

The focus control loop contains a digital PID controller which has 5 parameters that are available to the user.

These coefficients influence the integrating (foc\_int), proportional (foc\_lead\_length, part of foc\_parm3) and differentiating (foc\_pole\_lead, part of foc\_parm1) action of the PID and a digital low-pass filter (foc\_pole\_noise, part of foc\_parm2) following the PID. The fifth coefficient foc\_gain influences the loop gain.

#### 7.16.3.3 Dropout detection

This detector can be influenced by one parameter (CA\_drop). The FOK signal will become false and the integrator of the PID will hold if the CA signal drops below this programmable absolute CA level. When the FOK signal becomes false it is assumed, initially, to be caused by a black dot.

#### 7.16.3.4 Focus loss detection and fast restart

Whenever FOK is false for longer than approximately 3 ms, it is assumed that the focus point is lost. A fast restart procedure is initiated which is capable of restarting the focus loop within 200 to 300 ms depending on the programmed coefficients of the microcontroller.

### SAA7824

Product specification

#### 7.16.3.5 Focus loop gain switching

The gain of the focus control loop (foc\_gain) can be multiplied by a factor of 2 or divided by a factor of 2 during normal operation. The integrator value of the PID is corrected accordingly. The differentiating (foc\_pole\_lead) action of the PID can be switched at the same time as the gain switching is performed.

#### 7.16.3.6 Focus automatic gain control loop

The loop gain of the focus control loop can be corrected automatically to eliminate tolerances in the focus loop. This gain control injects a signal into the loop which is used to correct the loop gain. Since this decreases the optimum performance, the gain control should only be activated for a short time (for example, when starting a new disc).

#### 7.16.4 RADIAL SERVO SYSTEM

#### 7.16.4.1 Level initialization

During start-up an automatic adjustment procedure is activated to set the values of the radial error gain (re\_gain), offset (re\_offset) and satellite sum gain (sum\_gain) for TPI level generation. The initialization procedure runs in a radial open loop situation and is  $\leq$ 300 ms. This start-up time period may coincide with the last part of the motor start-up time period:

- Automatic gain adjustment: as a result of this initialization the amplitude of the RE signal is adjusted to within ±10% around the nominal RE amplitude

- Offset adjustment: the additional offset in RE due to the limited accuracy of the start-up procedure is less than ±50 nm

- TPI level generation: the accuracy of the initialization procedure is such that the duty factor range of TPI becomes 0.4 < duty factor < 0.6 (default duty factor = TPI HIGH/TPI period).

#### 7.16.4.2 Sledge control

The microcontroller can move the sledge in both directions via the steer sledge command.

#### 7.16.4.3 Tracking control

The actuator is controlled using a PID loop filter with user defined coefficients and gain. For stable operation between the tracks, the S-curve is extended over 75% of the track. On request from the microcontroller, S-curve extension over 2.25 tracks is used, automatically changing to access control when exceeding those 2.25 tracks.

Both modes of S-curve extension make use of a track-count mechanism. In this mode, track counting results in an 'automatic return-to-zero track', to avoid major disturbances in the audio output and providing improved shock resistance. The sledge is continuously controlled, or provided with step pulses to reduce power consumption using the filtered value of the radial PID output. Alternatively, the microcontroller can read the average voltage on the radial actuator and provide the sledge with step pulses to reduce power consumption. Filter coefficients of the continuous sledge control can be preset by the user.

#### 7.16.4.4 Access

The access procedure is divided into two different modes (see Table 14), depending on the requested jump size.

Table 14 Access modes

| ACCESS<br>TYPE | JUMP SIZE <sup>(1)</sup> | ACCESS<br>SPEED                              |  |

|----------------|--------------------------|----------------------------------------------|--|

| Actuator jump  | 1 – brake_distance       | decreasing velocity                          |  |

| Sledge jump    | brake_distance -32768    | maximum<br>power to<br>sledge <sup>(1)</sup> |  |

#### Note

1. The microcontroller can be preset.

The access procedure makes use of a track counting mechanism, a velocity signal based on a fixed number of tracks passed within a fixed time interval, a velocity set point calculated from the number of tracks to go and a user programmable parameter indicating the maximum sledge performance.

If the number of tracks remaining is greater than the brake\_distance then the sledge jump mode should be activated or, the actuator jump should be performed. The requested jump size together with the required sledge breaking distance at maximum access speed defines the brake\_distance value.

During the actuator jump mode, velocity control with a PI controller is used for the actuator. The sledge is then continuously controlled using the filtered value of the radial PID output. All filter parameters (for actuator and sledge) are user programmable.

#### Product specification

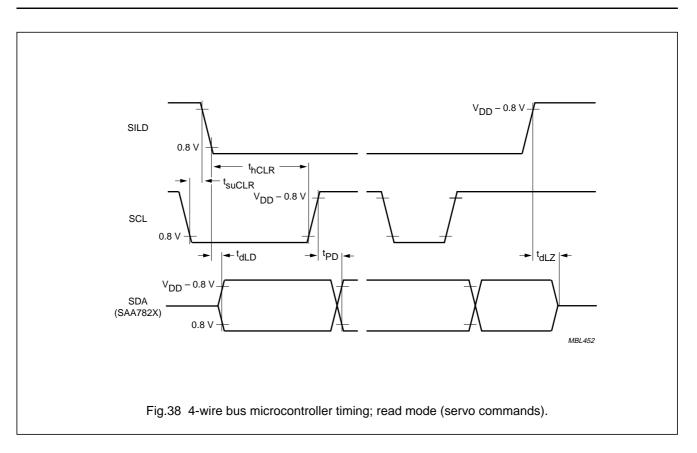

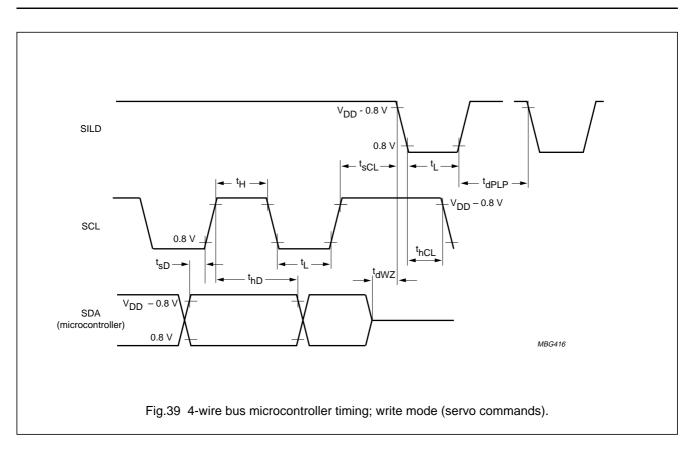

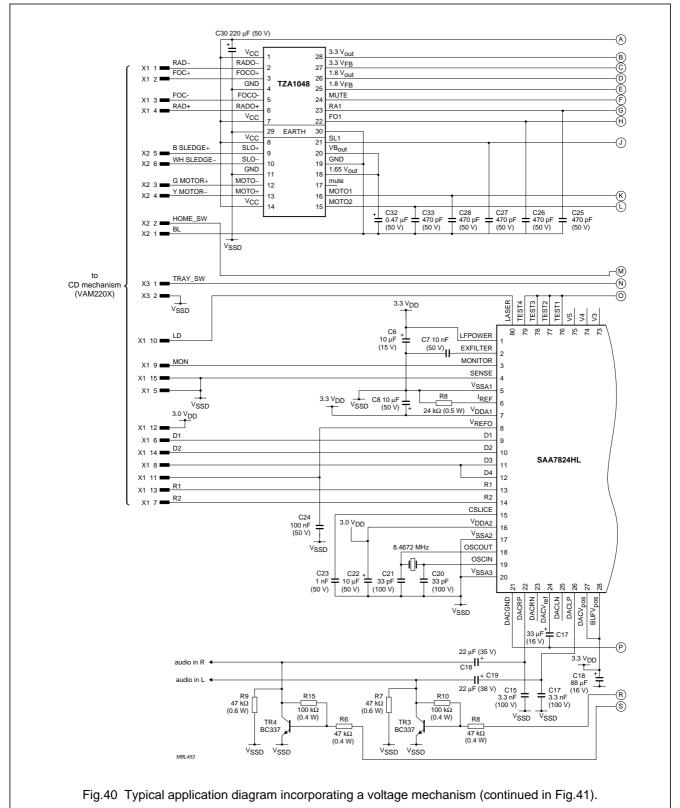

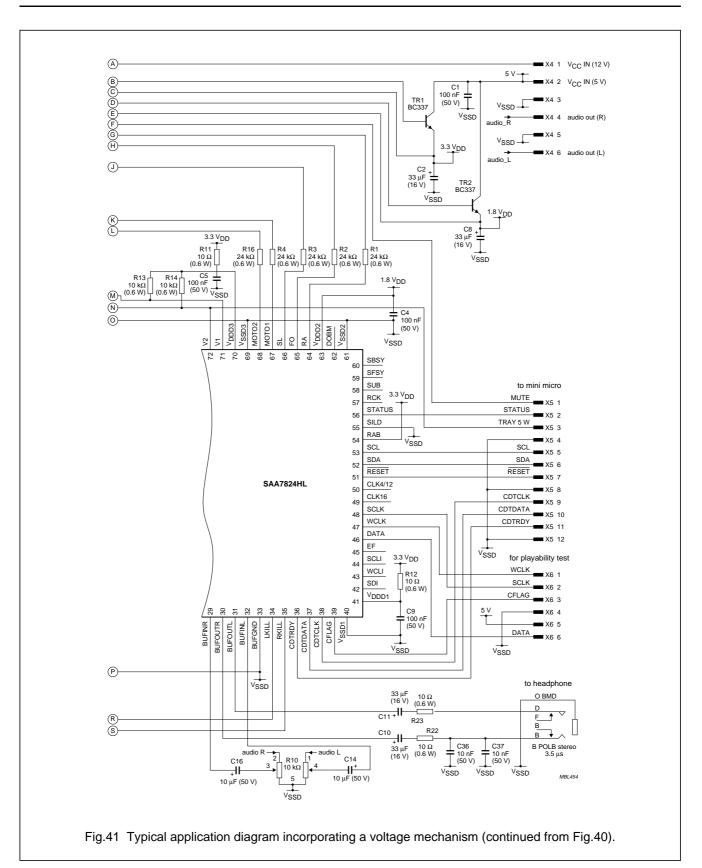

## CD audio decoder, digital servo and filterless DAC with integrated pre-amp and laser control